Pagina 6 di 11

Sistema di prova e metodologia di test

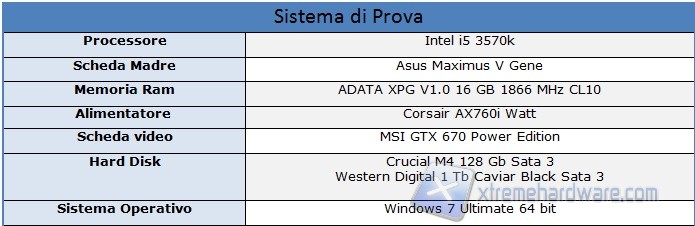

Abbiamo effettuato i nostri test con una piattaforma Intel LGA 1155, con CPU dotata di architettura Ivy Bridge. Nel dettaglio:

Ricordiamo che queste memorie hanno un Vdimm a default di 1,50V per la frequenza standard di 1866 Mhz, il quale viene impostato anche selezionando i profili XMP. Sulle CPU di architettura Ivy Bridge è necessario mantenersi massimo al Vdimm di 1,5V+5%, ovvero circa 1,57V, per evitare nel tempo di danneggiare il memory controller. Sicuramente con il kit AX3U1866XW8G10-2X di ADATA non dovremo preoccuparci di questo aspetto.

Vi ricordiamo inoltre cosa si intende per timing di accesso, i cui valori si possono impostare dal BIOS della scheda madre:

- CasLatency Time (TCL): durante un’operazione di lettura, rappresenta l'intervallo di tempo tra l'istante in cui il comando di lettura giunge ad una certa cella di memoria e quello in cui inizia il trasferimento dei dati. La denominazione è dovuta al fatto che, per individuare la cella di memoria, l'indirizzo di colonna viene selezionato sempre per ultimo (tramite il segnale Cas), successivamente a quello di riga.

- Ras to Cas Delay Time (TRCD): costituisce l'intervallo di tempo che passa tra l'attivazione della riga e della colonna che identificano la cella di memoria in cui si vuole leggere o scrivere il dato, cioè il ritardo del segnale Cas rispetto al segnale Ras.

- Ras Precharge Time (TRAS): rappresenta il periodo di tempo in cui una certa riga è attiva, prima che giunga il segnale precharge.

- RowPrecharge Timing (TRP): questo settaggio BIOS specifica il minimo ammontare di tempo tra due successive attivazioni allo stesso modulo DDR. Minore è l'intervallo, più velocemente il prossimo banco di memoria può essere attivato in fase di lettura o scrittura.